運算器能夠進行算術運算和邏輯運算。運算器的基本功能是完成對各種數據的加工處理,例如算術四則運算,與、或、求反等邏輯運算,算術和邏輯移位操作,比較數值,變更符號,計算主存地址等。運算器是計算機中處理數據的功能部件,對數據處理主要包括數據的算術運算和邏輯數據的邏輯操作;因此,實現對數據的算術與邏輯運算是運算器的核心功能。

本教程操作環境:windows7系統、Dell G3電腦。

運算器能夠進行算術運算和邏輯運算。

運算器:arithmetic unit,計算機中執行各種算術運算和邏輯運算操作的部件。

運算器由算術邏輯單元(ALU)、累加器、狀態寄存器、通用寄存器組等組成。算術邏輯運算單元(ALU)的基本功能為加、減、乘、除四則運算,與、或、非、異或等邏輯操作,以及移位、求補等操作。計算機運行時,運算器的操作和操作種類由控制器決定。運算器處理的數據來自存儲器;處理后的結果數據通常送回存儲器,或暫時寄存在運算器中。與Control Unit共同組成了CPU的核心部分。

運算器是計算機中處理數據的功能部件。對數據處理主要包括數據的算術運算和邏輯數據的邏輯操作。因此,實現對數據的算術與邏輯運算是運算器的核心功能。

運算器的基本功能是完成對各種數據的加工處理,例如算術四則運算,與、或、求反等邏輯運算,算術和邏輯移位操作,比較數值,變更符號,計算主存地址等。

運算器中的寄存器用于臨時保存參加運算的數據和運算的中間結果等。運算器中還要設置相應的部件,用來記錄一次運算結果的特征情況,如是否溢出,結果的符號位,結果是否為零等。

運算器的運算

加法器

一位全加器:

Si=Ai⊕Bi⊕CiCi+1=AiBi+(Ai⊕Bi)Ci

延遲運算: 與門、或門 1T;異或門3T

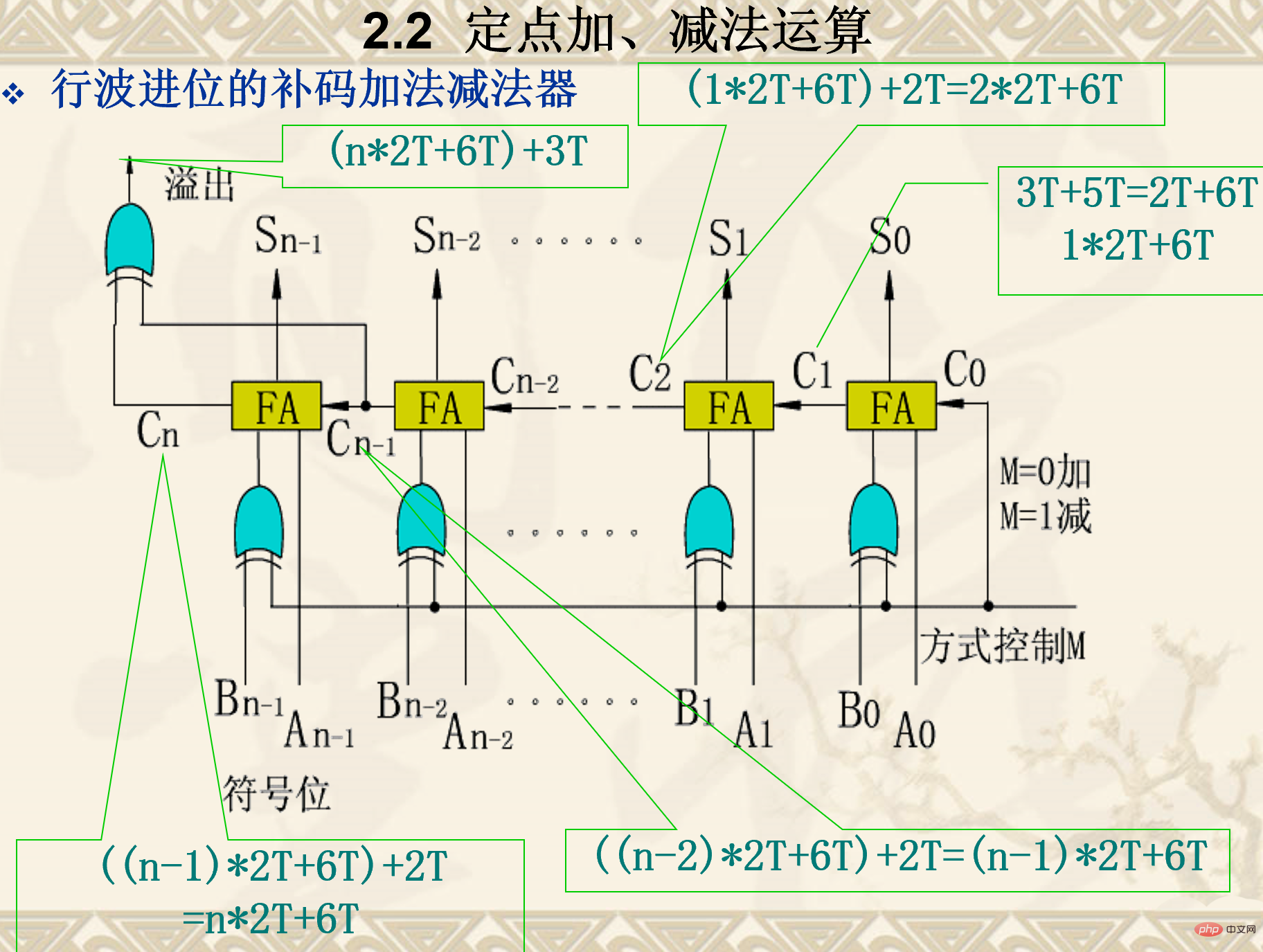

行波進位的補碼加法/減法器

當M=0時,B數各位經過0異或保持原數B不變,最低位進位為0,結果就是A與B相加;當M=1時,B數各位經過1異或取反,再結合最低位的進位1,結果就是A+(-B)= A-B

定點乘法

在定點計算機中,兩個原碼表示的數相乘的運算規則是:乘積的符號位由兩數的符號位按異或運算得到,而乘積的數值部分則是兩個正數相乘之積。

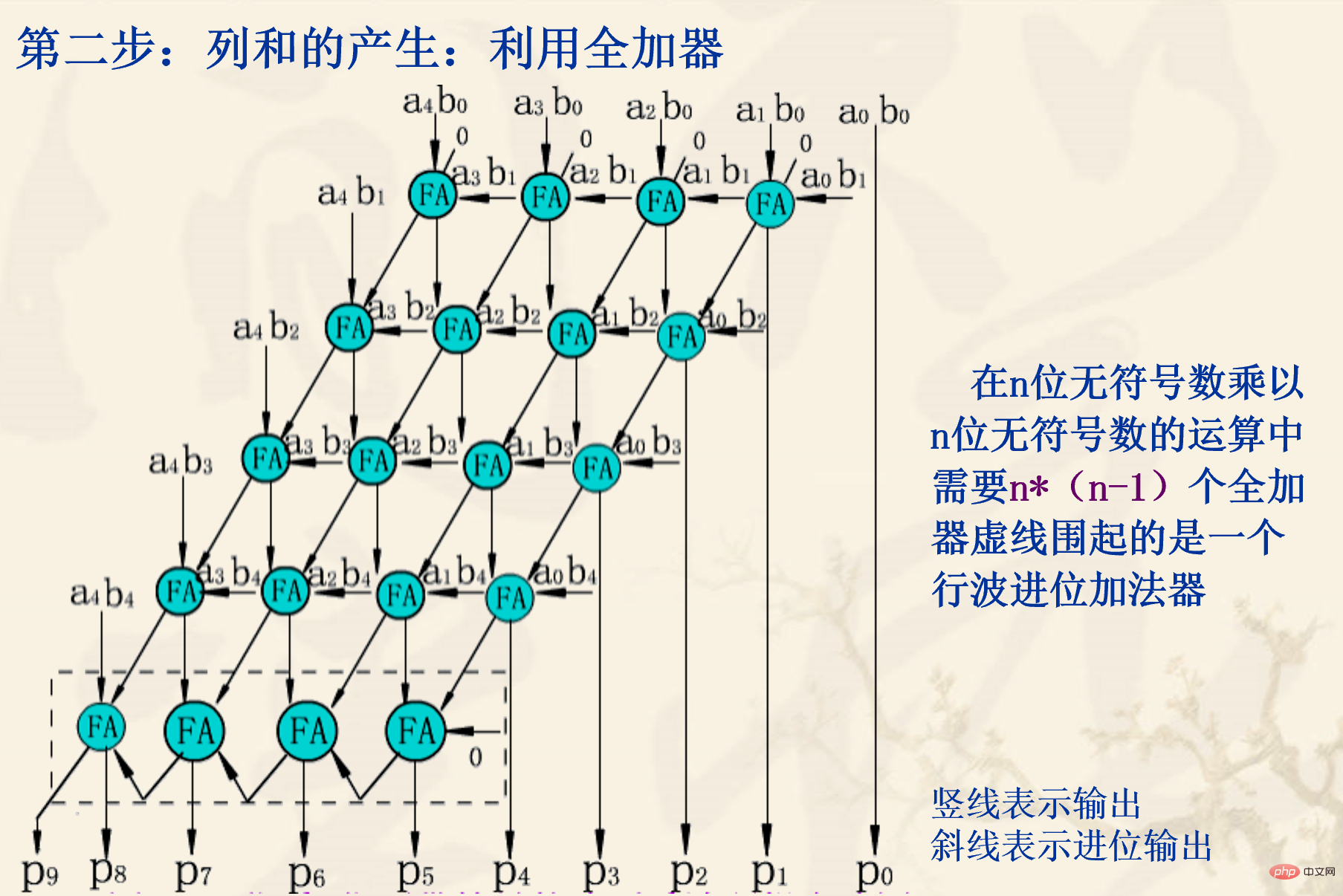

介于串行乘法器已經被淘汰,下面只介紹并行乘法器。并行乘法器的關鍵是快速產生n*n個位積,然后對位積進行相加運算產生n+n-1個列和。

并行乘法器:

第一步是并行計算nn個位積,為此需要nn個與門;

第二步是利用n*(n-1)個全加器計算列和。

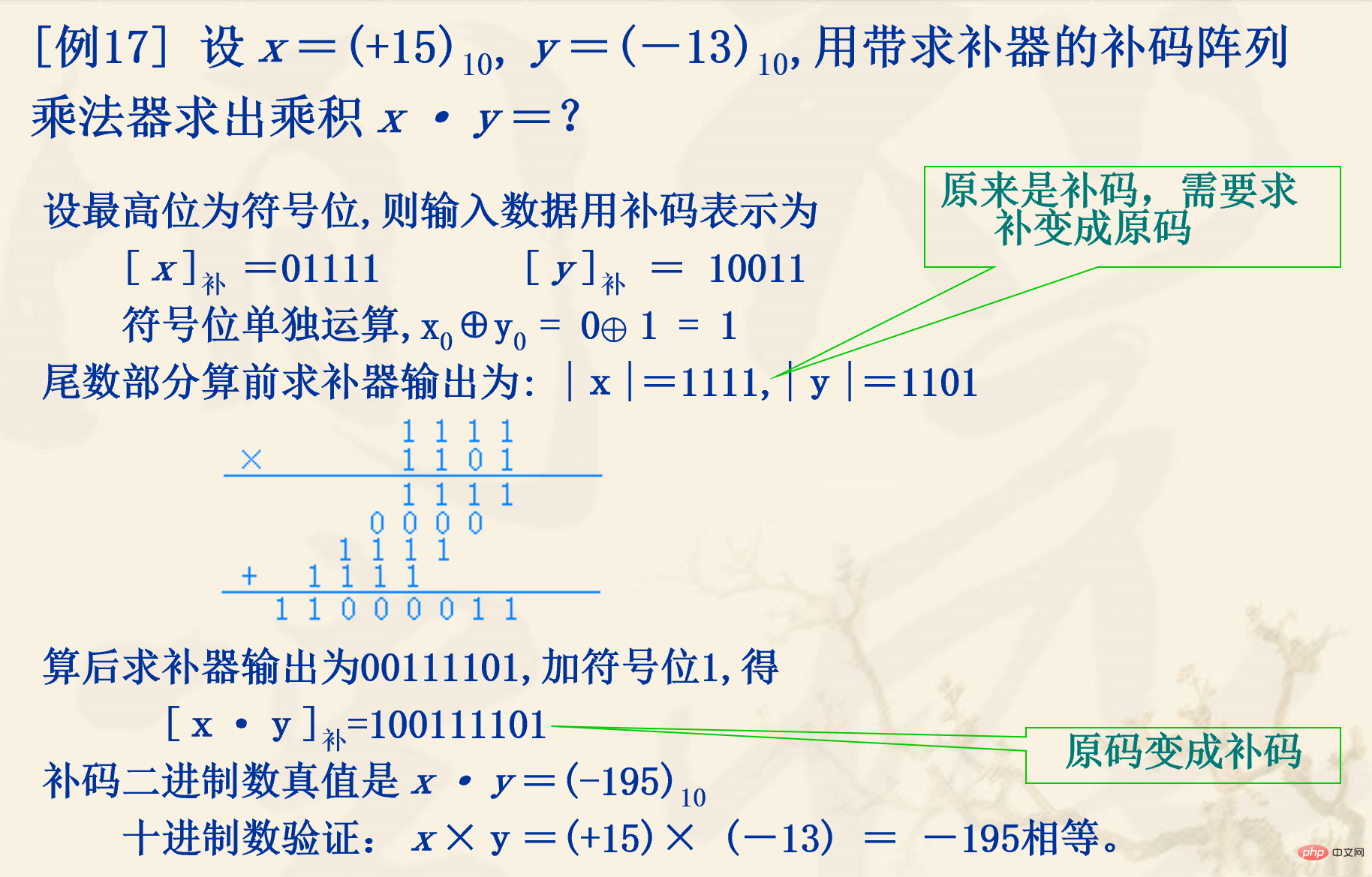

間接補碼乘法運算

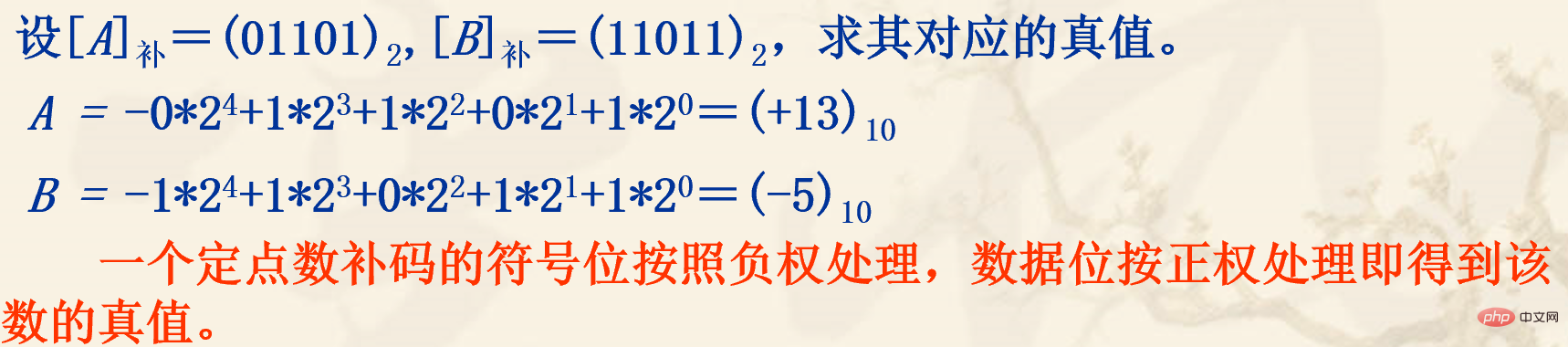

由于在計算機內數據是以補碼形式存在,必須考慮補碼乘法運算中由補碼、原碼之間簡便的互換運算

由補碼直接求原碼的運算:

正數的補碼不變,負數的補碼等于從右邊開始遇到的第一個真值的1以后除了符號位以外1變0,0變1。

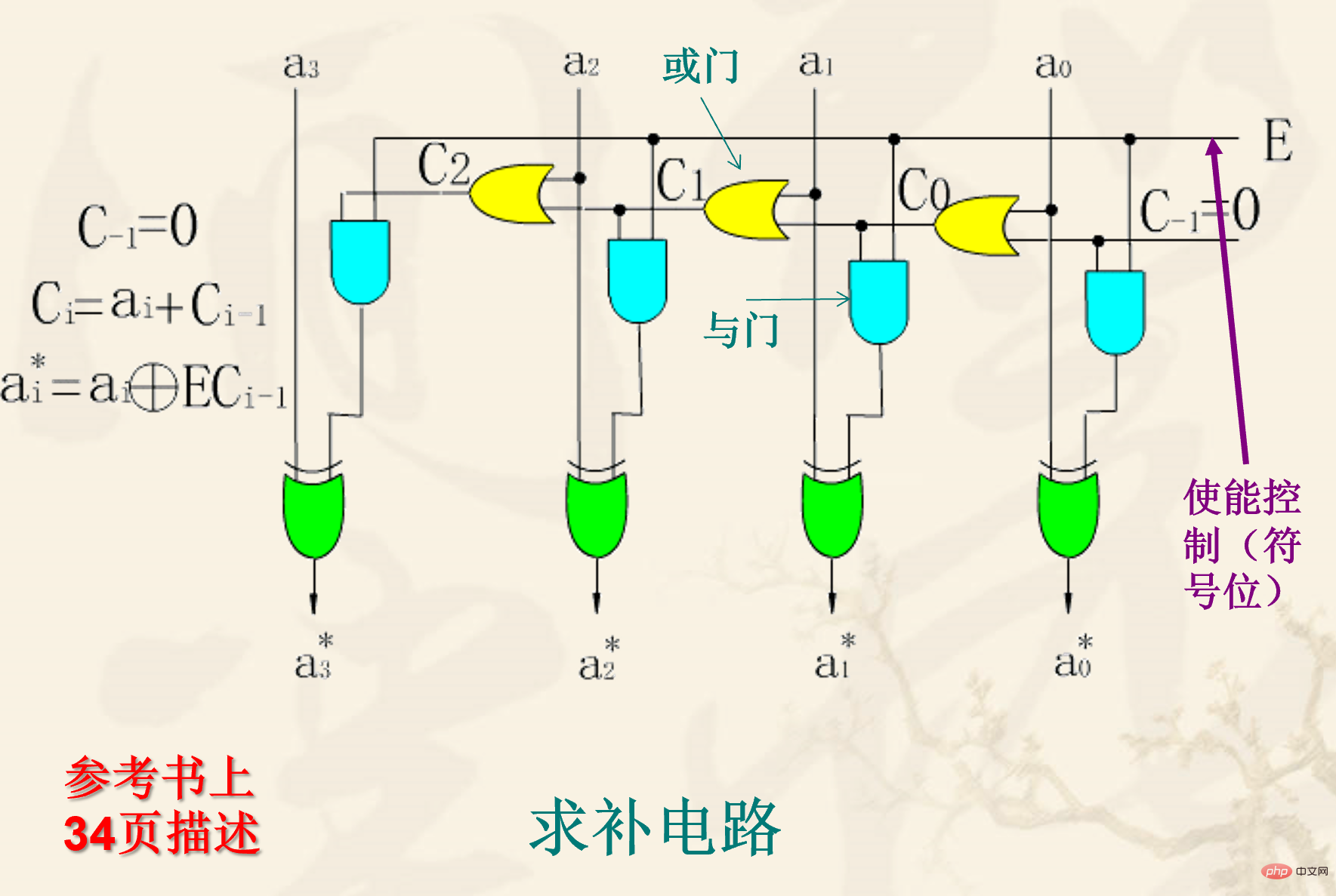

求補電路的思想:

如果符號位是0,數據不變

如果符號位是1,則符號位保持不變,數據位從lowbit(x)左邊除符號位以外全部求反

串聯的或門陸續接受來自低位的數字和上一次的或門輸出,一旦某一次低位數字為1,這一次的或門輸出及后續的或門輸出均為1。每一級的或門輸出都會與使能端E相與,當使能端E=1時,簡化為直接由或門輸出控制。與門輸出接異或門,當或門為1,E=1時,異或門發揮求反功能。當使能端為0時,各級異或門均為0,不發揮求反功能,即各位均保持不變。因此,可以將使能端接數的符號位。

間接補碼乘法器,即先將兩個數經過算前求補器轉化為原碼,然后經過乘法器,再將結果經過算后求補器轉化為補碼。

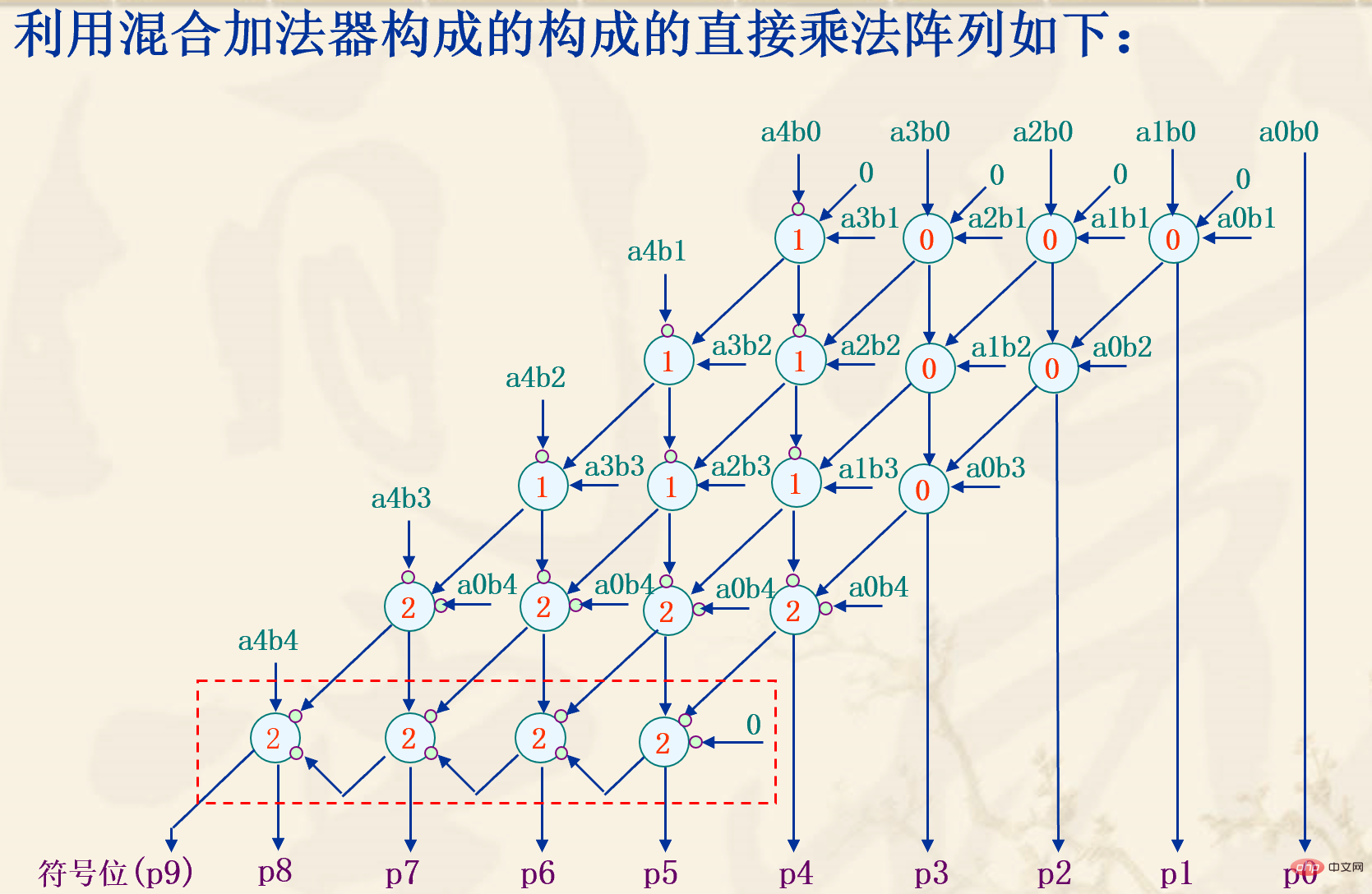

直接補碼乘法運算

根據這一特點,我們可以設計輸入帶有負權的加法器,用來構造直接補碼并行乘法器。根據帶有負權的輸入端數量,可以分為0,1,2,3四類加法器。用混合加法器構造出的并行乘法器如下圖:

站長資訊網

站長資訊網